It may have some condition wherein a flip-flop will not toggle its output if that condition is met. What is the frequency.

Low Power Design Techniques Vlsi4freshers

250 Vlsi Interview Questions and Answers Question1.

. In it FF1s output will remain stable as long as EN 0. So in a multi voltage design when there is a signal propagating from high to low voltage domains then it may lead to breakage of the dielectric layer if that voltage exceeds the breakdown voltage. What are the power dissipation components.

Design Uber or lyft a ride sharing service Design a service where a user requests a ride from the app and a driver arrives to take them to their destination. 4Questions on In rush current. After that it is easy to understand internal low-level design architecture.

What are the inputs and outputs from the power analysis. 30 Hardware Design Development Interview Questions and Answers Real-time Case Study Questions Frequently Asked Curated by Experts Download Sample Resumes. VLSI Interview Questions and Answers.

Prepare yourself for your interview at Power Design Inc. Questions based on resume followed by low power design questions. By browsing Interview questions and processes from real candidates.

How many memories were there in SOC. Both or one of these can be asked in the interview. How can you reduce power on chip.

What are the challenge you will see in lower technology. The principle behind clock gating is to stop the clock of those sequential elements whose data is not toggling. Low power design is a collection of techniques and methodologies aimed at reducing the overall dynamic and static power consumption of an integrated circuit IC.

For a question based on Low Level Design be sure to come up with a Logical View and a Process View. As you might already know there can be 2 types of design - Low level and high level designs. You will also learn about high-level design low-level design and Database design in this masterpiece.

On the right hand side its equivalent. DFT is a technique that makes test generation and test application easier and cost effective. In this article we are going to discuss the 5 main tips for low-level design which is helpful to crack the interview.

This technology becomes popular mainly because of its low power requirements and quick response. PowerApps Interview Questions and Answers. What kind of testcases did you develop.

Types of checks that can be done in Prime Time. Why metal density rules are important. DFT techniques help in making the internal flip-flop easily controllable and observableControllable means you can initialize them into any value you want and.

250 Physical Design Engineer Interview Questions and Answers Question1. At its core it is a suite of data platforms connectors services and apps that offer a quick application development. It enables you to create mobile apps that run on different operating systems such as Windows iOS and Android.

Types of circuits required to implement low power design-level shiftersisolations cells etc. Clock gating is a very common technique to save power by stopping the clock to a module when the module is not operating. Power Dissipation In CMOS.

Questions based on resume followed by low power design questions. How do you validate your floorplan and what analysis you do during floorplan. Power planning related questions for interview.

Explain one testcase flow in detail. Digital Design Interview Questions Part 4. PowerApps is a Platform as a Service.

What does it mean the channel is pinched off. The power plant uses the form of energy such as coal diesel and converts it into electrical energy. One of the major drawbacks is it cannot be repaired once any fault occurs in them.

As discussed in Clock switching and clock gating checks there are two kinds of clock gating checks at combinational gatesWe also discussed that for an AND type check enable must launch from a negative edge-triggered flip-flop and for an OR type check. How can you reduce power on chip. Why does the present VLSI circuits use MOSFETs instead of BJTs.

Not only buck converter the interviewer may ask you to draw other fundamental topologies too So you should be familiar with other basic topologies like Flyback Boost Buck-boost. Dynamic Power Leakage power. How memory preloading works.

In testing of sequential circuits it is difficult to control and observe the internal flops. RTL level code talks only about data transfer. Dynamic Power Leakage power.

How to reduce them. Transmission gate is a non-restoring circuit because if the input to transmission gate is a noisy or otherwise degraded signal the output will receive the same noise. Types of circuits required to implement low power design-level shiftersisolations cells etc.

Efficient storage and search for posts or tweets. What is list file MPF file scatter file. Low Power Design Techniques.

What are the checks after power planning is completed. 1 What is the Power plant or Power Station. The generation distribution and transmission system together constitute a network called as Power plant.

-It may be power planning- because you found more IR drop-It may be low power target-because you had more dynamic and leakage power-It may be macro placement-because it had more connection with standard cells or macros-It may be CTS-because you needed to handle multiple clocks and clock domain crossings. Basics Of UVMTestbench Architecture. When a signal is propagating from lower to higher voltage domains than it may happen that.

What is threshold voltage. What are the various regions of operation of MOSFET. Computer Architecture Interview Questions Part 2.

How are those regions used. Figure 1 below shows such a condition. Why power stripes routed in the top metal layers.

Why transmission gate TG is called non-restoring circuit. No right or wrong answer for the Design Question. Did you find any bugs issues in the rtl 17.

The main goal of low-level design is to design the internal logical design for code. A frequently asked interview question in. In most of the power electronics interview questions you are going to face this basic question.

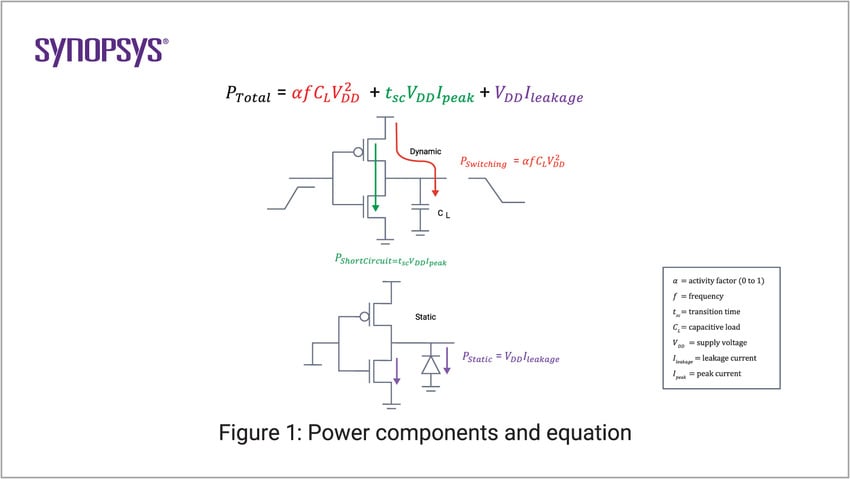

ASIC synthesis 38 Synthesis 38 verilog interview questions 30 Verification 28 ASIC 26 DSP 22 HDL 19 Static Timing Analysis STA 18 Low Power Techniques 16 logic synthesis 16 FPGA 15 MATLAB 15 Timing Analysis 15 Physical Design 13 Digital design 9 CMOS 8 Asynchronous FIFO 7 interview 7 3-D ICs 6 PIC. Looking at the individual components of power as illustrated by the equation in Figure 1 the goal of low power design is to reduce the individual components of power as. Thats all about some of the frequently asked System Design Interview Questions for Java.

Breakdown voltage is very large than the supply voltage. An example of the power system is a grid that supplies power to the other system. MOSFET Interview Questions Part 1 March 14 February 6 January 11 2019 17.

Low Power Design Techniques Vlsi4freshers

Digital Design Expert Advise Low Power Design And Verification

Low Power Design Techniques Vlsi4freshers

Digital Design Expert Advise Low Power Design And Verification

Low Power Design Techniques Vlsi4freshers

Digital Design Expert Advise Low Power Design And Verification

Low Power Design Techniques Vlsi4freshers

What Is Low Power Design Techniques Methodology Tools Synopsys

0 comments

Post a Comment